## 图学年度 國立成功大學工程科学系 电子电路 試題 共一頁

## 請按題號順序作答 (每題分數 20 分)

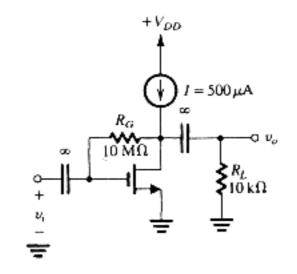

- 1. In the circuit of Fig. 1, the NMOS transistor has  $|V_i| = 0.9 \text{ V}$  and  $|V_a| = 50 \text{ V}$ , and operates with  $|V_o| = 2 \text{ V}$ .

- (a) What is the voltage gain  $v_{\alpha}/v_{z}$ ?

- (b) What do V<sub>n</sub> and the gain become for I increased to 1 mA?

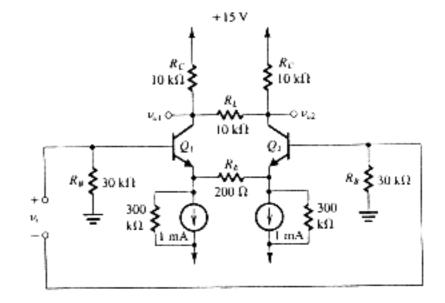

- 2. For the differential amplifier shown in Fig. 2, find

- (a) the differential gain,

- (b) the differential input resistance,

- (c) the common-mode gain, and

- (d) the common-mode input resistance.

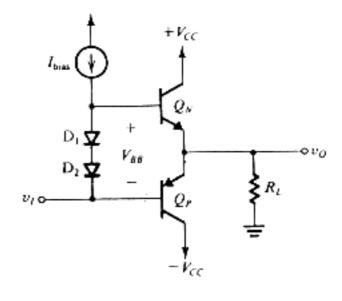

- 3. A class AB output stage using a two-diode bias network as shown in Fig. 3 utilizes diodes having the same junction area as the output transistors. For V<sub>Cl</sub> = 10 V, I<sub>bias</sub> = 0.5 mA , R<sub>L</sub> = 100 Ω , β<sub>N</sub> = 50 , and |V<sub>Clisat</sub>| = 0 V, what is the quiescent current? What are the largest possible positive and negative output signal levels? To achieve a positive peak output level equal to the negative peak level, what value of β<sub>N</sub> is needed if I<sub>bias</sub> is not changed? What value of I<sub>bias</sub> is needed if β<sub>N</sub> is held at 50?

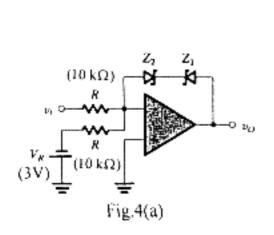

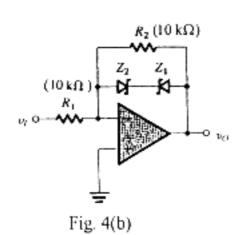

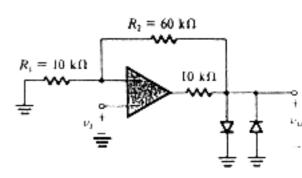

- 4. For the circuits in Figs. 4(a) to 4(c), sketch and label the transfer characteristic v<sub>O</sub> v<sub>I</sub>. Denoting the zener voltages of Z<sub>1</sub> and Z<sub>2</sub> by V<sub>Z1</sub> = 6 V and V<sub>Z2</sub> = 4 V and assuming that in the forward direction the voltage drop is approximately 0.7 V. The diodes are assumed to have a constant 0.7 V drop when conducting. The op amp saturates at ±12 V.

- Design a Chebyshev filter that meets the following low-pass specifications: f<sub>p</sub> = 3.4 kHz, f<sub>s</sub> = 4 kHz,

A<sub>max</sub> = 1 dB, and A<sub>max</sub> = 35 dB. Find the required order N, the poles, and the transfer function T(s).

Fig. 1

Fig. 2

Fig. 3

Fig. 4(c)