135 # 3 頁 第 1 頁 國立成功大學九十九學年度碩士班招生考試試題

系所組別: 工程科學系甲、戊、已組

緩跳

電子電路 考試科目 新秋日期:0307·新次:1

※ 考生請注意:本試類 ▽□ □ □ 不可 使用計算機

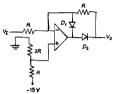

1. In Fig. 1, the diodes and the op-amp are ideal. (a) Plot the transfer characteristic. (6 分) (b) Plot the waveform of  $V_O$  when  $V_f = 15\sin(4\pi t)$ . (5 %)

Fig. 1

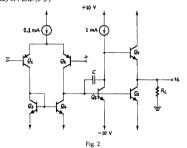

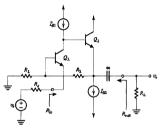

Figure 2 shows a circuit suitable for op-amp application. For all transistors β=100, V<sub>RE</sub>=0.7 V.

$|V_r| = 25$  mV, and  $r_a = \infty$ . (a) For inputs grounded and output held at 0 V, find the emitter currents of all transistors (you can ignore base currents for dc analysis). (4 分) (b) Calculate the gain of the amp with a load of 10 kΩ. (8 分) (c) With load as in (b), calculate the value of the capacitor C required for a 3-dB frequency of 1 kHz. (6 分)

(背面仍有題目.請繼續作答)

系所組別 工程科學系甲、戊、己組

考試科目: 雷子雷路

考駄日期:0307・約次:1

## ※ 考生請注意:本試願 ▽「□不可 使用計算機

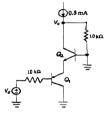

3. Analyze the circuit in Fig. 3. The transistors are biased by a current source such that the transistors have β=100, r<sub>s</sub>=5 kΩ, g<sub>s</sub>=20 mA/V, r<sub>s</sub>=∞, C<sub>s</sub>=2 pF, and C<sub>s</sub>=6 pF (a) Find the midband gain: (7 %) (b) Find f<sub>tt</sub> by using the open-circuit time constant • (8 %)

Fig. 3

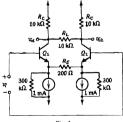

4. For the diff. amp in Fig. 4, (a) Sketch the differential half-ckt and the common-mode half-ckt. (8 分) (b) Find the differential gain, the differential input resistance, the common-mode gain, and the common-mode input reistance. Assume that β = 100, V<sub>f</sub>=25 mV, and V<sub>s</sub> = ∞. (12 分) +15 V

Fig. 4

系所組別 工程科學系甲、戊、己組

不用他加 工任行字系中、以、CN 考試科目 電子電路

編號 135

考账日期:0307·節次:1

## ※ 考生請注意:本試題 ☑可 □不可 使用計算機

In Fig. 5, the transistors are assumed to have common-emitter current gain β, emitter resistance r<sub>e</sub>, and early voltage V<sub>A</sub>=∞. Find expressions for A<sub>f</sub> ≡ v<sub>g</sub>/v<sub>g</sub>, R<sub>B</sub>, and R<sub>mg</sub>. (20 分)

Fig. 5

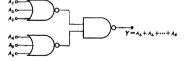

6. In Fig. 6, an approach realizing the OR function of six input variables is shown. (a) Sketch the CMOS realization for the logic gates in the figure · (6 %) (b) Assuming that the transistors in the circuit are properly sized to provide each gate with a current-driving capability equal to that of the basic matched inverter, find the number of transistors and the total area. Assume that the basic inverter has the (W/L)<sub>n</sub> ratio of 1.2 µm / 0.8 µm and the (W/L)<sub>n</sub> ratio of 3.6 µm / 0.8 µm \* (10 %)

Fig. 6