## 國立成功大學 8%學年度 電機所考試(計算物概論試題) 第1頁

The total score of this examination is 100. The score of each question is indicated in a pair of parentheses.

- 1. (10) Explain the following terms.

- (a) (2) Vector machine

- (b) (2) Microinstruction

- (c) (2) Two-way set-associative cache

- (d) (2) Memory interleaving

- (e) (2) Bus-grant line

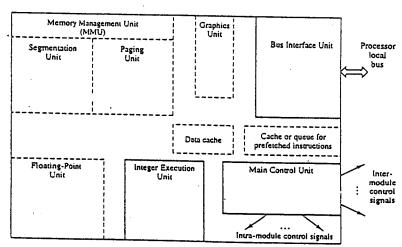

- 2. (10) The internal architecture of a modern microprocessor is shown below.

Figure I. . Internal components of a microprocessor. (Components within dashed lines are found in some but not all microprocessors.)

- (a) (6) Give at least three reasons to explain why it is more powerful than before.

- (b) (4) What functions can the MMU perform?

- 3. (10) Assume that a computer has eight pages of virtual memory, four page references (i.e., with successive references to the same page omitted):

- $\begin{smallmatrix} 1 & 4 & 6 & 1 & 5 & 7 & 1 & 6 & 3 & 2 & 7 & 3 & 2 & 6 & 0 & 2 & 3 & 1 & 4 & 3 & 1 & 5 & 7 & 5 & 3 & 2 & 5 & 4 & 2 & 6 & 4 & 2 & 3 & 6 & 1 & 5 & 3 \\ \end{smallmatrix}$

For each of the following page-replacement policies, determine (a) the sequence of pages loaded, and (b) the number of page faults.

- (a) (5) LRU The CPU replaces the least recently used page.

- (b) (5) FIFO The CPU replaces the oldest (least recently loaded) page in the set.

- 4. (10) Assume we want to design a microprocessor-based 4½ digital volt meter and connect it to our PC. Inside this meter a single-chip microprocessor such as Intel 8052 is used as the controller.

## 國立成功大學 80學年度 意提所考試(計算的抵倫試題)共 2頁

- (a) (3) Use a block diagram to describe the hardware architecture of this volt meter.

- (b) (3) Use a flow chart to show the software structure of this meter.

- (c) (4) Explain how to connect this meter to a PC and how the PC gets the data.

- 5. (10) An even parity checker which counts the number of 1's in a bit-serial input stream and assert its output when the input stream contains an even number of 1's. Design this logic circuit by first giving the state diagram and then implement it using a D flip-flop.

- 6. (12)

- (a) (5) Derive a formula for the maximum number of nodes on level i of a binary tree. Use induction to prove the correctness of your formula.

- (b) (7) Derive a formula for the number of different binary trees that have only one leaf and have a depth of k. Use induction to prove the correctness of the formula.

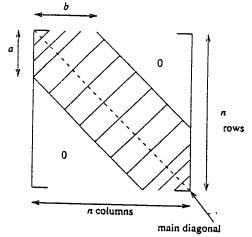

- 7. (16) A generalized band matrix  $D_{n,a,b}$  is an  $n \times n$  matrix in which all the nonzero terms lie in a band made up of a-1 diagonals below the main diagonal, the main diagonal, and b-1 diagonals above the main diagonal as shown in the figure below.

- (a) (3) How many elements are there in the band of  $D_{n,a,b}$ ?

- (b) (4) What is the relationship between i and j for the elements  $d_{i,j}$  of  $D_{n,a,b}$ ?

- (c) (5) Assume that the band of  $D_{n,a,b}$  is stored sequentially in an array e[k] by diagonals, starting with the lowermost diagonal, where k is the number of elements in the band. Write a C function value(n, a, b, i, j, e) that determines the value of element  $d_{ij}$  in the matrix  $D_{n,a,b}$ .

- (d) (4) Give a situation where you may use a generalized band matrix to represent some data.

- 8. (12) Assume a sequence has the following characteristic: A(0) = 2, A(1) = 3, and A(n) = A(n-1) + A(n-2) for n > 1. Write a recursive C program to generate the first k items of the sequence, where k should be provided by the user. Determine the time and memory complexities of your program.

- 9. (10) Define a *T-order* as a linear ordering of the vertices of a directed graph such that, for any two vertices *i*, *j*, if *j* is a predecessor of *i* in the graph then *i* precedes *j* in the linear ordering. Write a linear time algorithm to generate a *T-order* of the vertices of a directed graph. Clearly describe the data structure you use.