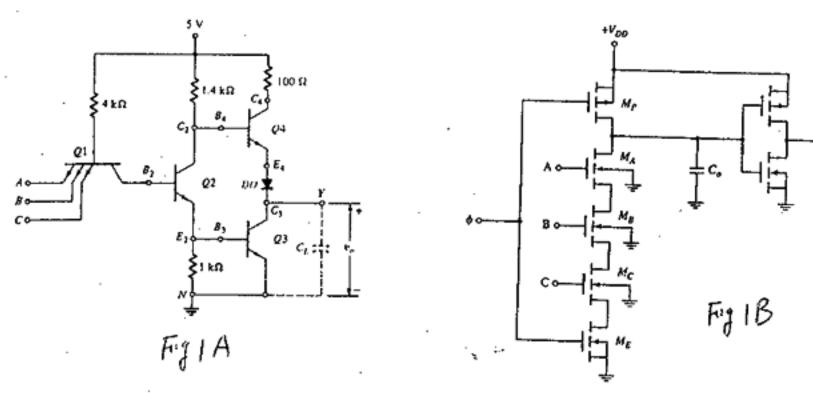

- (a) A TTL NAND gate with a totem-pole output is shown in Fig./A. Please estimate the (a) average static power dissipation P<sub>(av)</sub>, and (b) dynamic power dissipation P<sub>(dyn)</sub> of this gate. (/f%)

- (b) A domino logic circuit is shown in Fig./B. What is the function realized at the output Y?

(5%)

(A) 簡述(a)振盪器之振盪如何啓動?振盪器之優劣如何判斷?(4%),(b)動態 負電阻振盪器之操作原理(3%)?(c) Op-Amp 虚短路成立之條件(3%)。

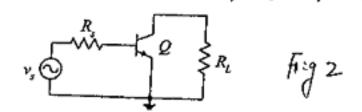

(B) 求圖 之 所示放大電路之頻率增益乘積(GBP)值與截止頻率。設 R<sub>i</sub> = 0.25 kΩ, R<sub>i</sub> = r<sub>x</sub> = 1 kΩ, C<sub>x</sub> = 100 pF, C<sub>y</sub> = 1 pF, β = 100。(10%)

- 一簡述(a)頻率補償之意義及目的。(b)試利用波德圖說明如何判斷網路系統之穩定與不穩定。(10%)

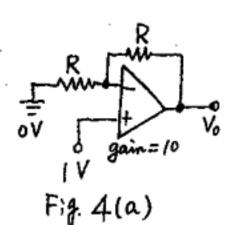

- (a) Calculate V<sub>-</sub> and V<sub>o</sub> of the circuit shown in Fig. 4(a) where the OPAMP gain = 10. (8%)

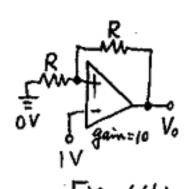

(b) Calculate V<sub>+</sub> and V<sub>o</sub> of the circuit shown in Fig. 4(b) where the OPAMP gain = 10. (9%)

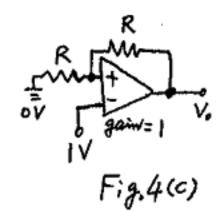

(c) Calculate V<sub>+</sub> and V<sub>o</sub> of the circuit shown in Fig. 4(c) where the OPAMP gain = 10. (8%)

(V<sub>-</sub>, V<sub>+</sub>, and V<sub>o</sub> are the inverting input voltage, noninverting input voltage, and output voltage of the OPAMP, respectively)

電る

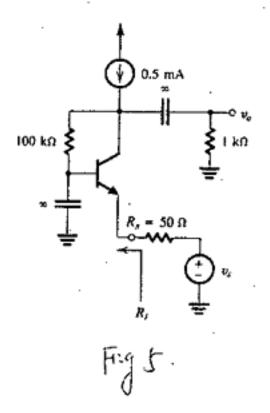

- 5. For the circuit shown in Fig. 5, find the input resistance Ri and the voltage gain  $v_{\sigma}/v_{\sigma}$ . Assume that the source provides a small signal  $v_{\sigma}$  and that  $\beta$  is high. Note that a transistor remains in the active region even if the collector voltage falls below that of the base by 0.4V or so. (10%)

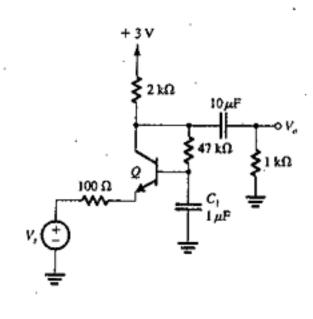

- 6. For the common-base circuit shown in Fig. 6, assuming the bias current to be about 1 mA,  $\beta=100$ ,  $C_p=0.8 \text{pF}$ , and  $f_7=600 \text{MHz}$ . Please (a) estimate the midband gain  $V_o/V_s$ .

- (b) use the short circuit time constants method to estimate the lower 3dB frequency  $f_L$ .

- (c) Find the high frequency poles, and estimate the upper 3dB frequency  $f_{H}$  (15%)

Fig 6