#### 编號: 190, 191, 204

### 國立成功大學一〇一學年度碩士班招生考試試題

共3頁,第/頁

系所組別: 電機工程學系甲、乙、丁、戊組、微電子工程研究所、電腦與通信工程研究所丙、丁組 考試科目: 電子學 考試日期:0226、節次:1

※ 考生請注意:本試題可使用計算機,並限「考選部核定之國家考試電子計算器」機型

- 1. Determine true or false for statements related to devices BJT and MOSFET. If false, please briefly explain to get full credits. (12%)

- (1) BJT and MOSFET are both three-terminal devices.

- (2) The emitter current of BJT is solely controlled by the BASE terminal while the drain-to-source current of MOSFET is only controlled by the GATE terminal.

- (3) The current of BJT and MOSFET in active mode/saturation region are both driven by majority carriers in the respective device.

- (4) Generally speaking, the current driving strength of BJT device is stronger than that of MOSFET with the same device dimension.

- (5) There are parasitic diodes in both BJT and MOSFET devices.

- (6) Einstein relationship can be applied to both BJT and MOSFET devices.

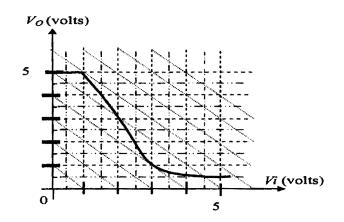

- A particular MOS inverter has the following transfer characteristic curve as shown in Fig.

, where Vo is the output voltage and Vi is the input voltage. What are the values for V<sub>OH</sub>,

V<sub>OL</sub>, V<sub>IH</sub>, V<sub>IL</sub>, NM<sub>H</sub> and NM<sub>L</sub> that are used to define noise margin? (8%)

- For the MOSFET circuit shown in the Fig. 2, determine the specified output voltage under difference cases. Consider the long-channel process technology for which |V<sub>tn</sub>| =|V<sub>tp</sub>|= 1 V, t<sub>ox</sub> = 8 nm, μ<sub>n</sub> = 450cm<sup>2</sup>/V•s, μ<sub>p</sub> = 150cm<sup>2</sup>/V•s, ε<sub>ox</sub> = 4.0×10<sup>-11</sup>F/m, (W/L)<sub>1</sub> = 4µm/0.8µm, V<sub>DD</sub> = 5V. The subscript 1 & 2 stand for parameters related transistor Q1 & Q2, respectively. Channel-length modulation effect can be ignored here. (13%)

- (a) What are the values of  $k'_n$  and  $k'_p$  including their unit?

- (b) Assume  $k'_{p}(W/L)_{2} = k'_{n}(W/L)_{1}$ , find  $\mathcal{V}_{0}$  when  $\mathcal{V}_{1} = 0V$  and  $\mathcal{V}_{1} = 5V$ , respectively.

- (c) Assume  $k'_{p}(W/L)_{2} = 0.01k'_{n}(W/L)_{1}$ , find  $\mathcal{V}_{0}$  when  $\mathcal{V}_{1} = 2.5V$ .

(背面仍有題目,請繼續作答)

## 編號: 190, 191, 204 **國立成功大學一〇一學年度碩士班招生考试試題** 共 3頁, 第2頁 系所組別: 電機工程學系甲、乙、丁、戊組、微電子工程研究所、電腦與通信工程研究所丙、丁組 考試4目: 電子學 考試日期: 0226 節次: 1

※ 考生請注意:本試題可使用計算機,並限「考選部核定之國家考試電子計算器」機型

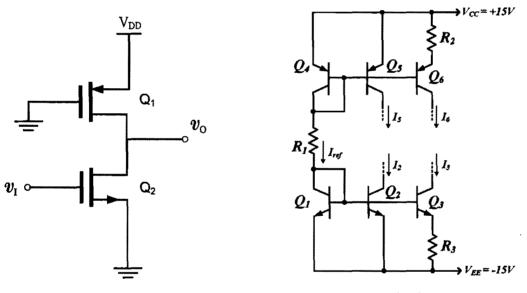

- For the circuit shown in Fig. 3, the relative transistors areas are A<sub>Q1</sub>=A<sub>Q2</sub>=A<sub>Q3</sub>=A<sub>Q4</sub>=A<sub>Q6</sub>=1. Assume that v<sub>BE</sub>≅0.7V and β is very large for all transistors. Please find the value of resistors (R<sub>1</sub>, R<sub>2</sub> and R<sub>3</sub>) and A<sub>Q5</sub> to achieve I<sub>2</sub>=1mA, I<sub>3</sub>=50µA, I<sub>5</sub>=3mA, and I<sub>6</sub>=100µA. (12%)

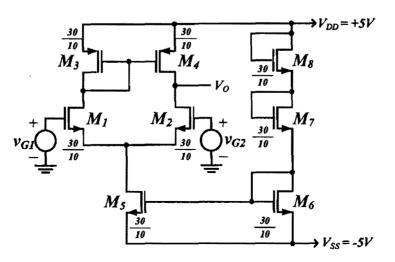

- 5. An active-loaded MOS differential amplifier is shown in Fig. 4. The NMOS transistor parameters are V<sub>t</sub>=+2V, V<sub>A</sub>(channel length modulation voltage)=-40V, and V<sub>GS</sub>=+4V at I<sub>D</sub>=1mA; The PMOS transistor parameters are V<sub>t</sub>=-3V, V<sub>A</sub>=+40V, and V<sub>GS</sub>=-6V at I<sub>D</sub>=1mA. Please calculate G<sub>m</sub>, R<sub>o</sub>(output resistance), A<sub>d</sub> (differential gain), and A<sub>c</sub> (common-mode gain) (12%).

Fig. 4

#### 國立成功大學一〇一學年度碩士班招生考試試題

共3頁,第3頁

系所組別: 電機工程學系甲、乙、丁、戊組、微電子工程研究所、電腦與通信工程研究所丙、丁組 考試科目: 電子學

考試日期:0226,節次:1

# ※ 考生請注意:本試題可使用計算機,並限「考選部核定之國家考試電子計算器」機型

- 6. A single-pole op amp has a dc gain of 100 dB and a unity-gain frequency of 10 MHz.

- (a) What is the upper-cutoff frequency of the op amp itself? (3%)

- (b) If the op amp is used to build a noninverting amplifier with a closed-loop gain of 60 dB, what is the bandwidth of the feedback amplifier? (3%)

- (c) Write an expression for the transfer function of the noninverting amplifier. (3%)

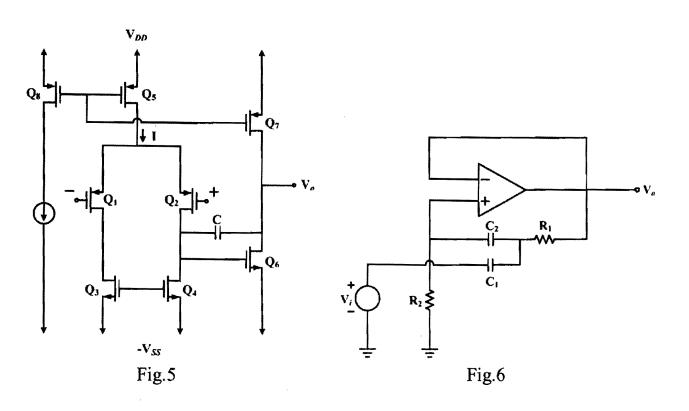

- 7. A two-stage CMOS Opamp circuit is shown in Fig. 5,  $\pm 1.65$  V power supplies are used and all transistors except for Q<sub>6</sub> and Q<sub>7</sub> are operated with overdrive voltages of 0.2 V magnitude; Q<sub>6</sub> and Q<sub>7</sub>, use overdrive voltages of 0.5 V magnitude. The fabrication process provides V<sub>tn</sub> =  $|V_{tp}| = 0.5$  V. If the first-stage bias current I = 200  $\mu$ A, C = 1.6 pF.

- (a) Find the input common-mode range and the range allowed for  $V_0$ . (6%)

- (b) Draw the simplified circuit model for the slewing process. (5%)

- (c) Calculate the slew rate of this Opamp. (5%)

編號:

190, 191, 204

- 8. Consider a circuit as shown in Fig. 6 assuming the Opamp to be ideal. Let  $C_1 = 0.001 \ \mu\text{F}$ ,  $C_2 = 0.0047 \ \mu\text{F}$ ,  $R_1 = 10 \ \text{k}\Omega$ ,  $R_2 = 20 \ \text{k}\Omega$ .

- (a) Derive the transfer function  $V_o/V_i$ . (9%)

- (b) Plot the frequency response of the transfer function and explain the function of this circuit. (9%)