編號:

165

# 國立成功大學一○○學年度碩士班招生考試試題

共 3 頁 第 / 頁

系所組別: 奈米科技暨微系統工程研究所

考試科目: 電子電路學

考試日期:0219,節次:1

# ※ 考生請注意:本試題 □可 ☑不可 使用計算機

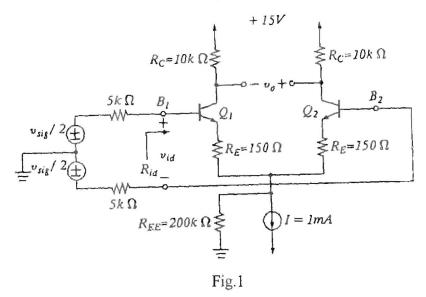

## 1. (15%)

For the circuit shown in Fig.1, evaluate the following ( $\beta$ =100):

- (a) The input differential resistance Rid.

- (b) The overall differential voltage gain  $v_0 / v_{\text{sig}}$  (neglect the effect of  $r_0$ )

- (c) The worst-case common-mode gain if the two collector resistances are accurate to within ±1%.

- (d)The CMRR, in dB

- (e) The input common-mode resistance (assuming that the Early voltage  $V_A=100V$ ).

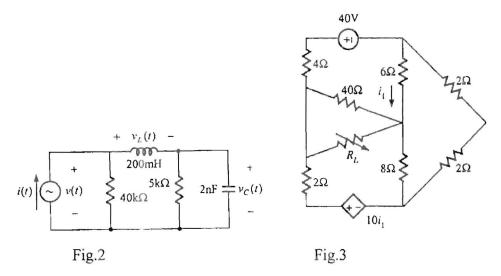

# 2. (15%)

The network in Fig.2 has  $i(t) = 10\cos(50000t)$  mA. Find the steady-state voltages v(t),  $v_L(t)$ , and  $v_C(t)$ .

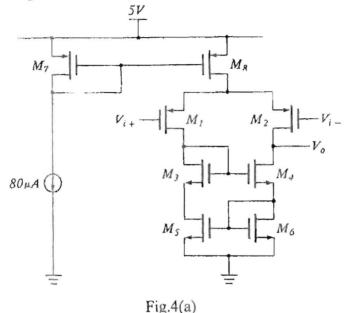

#### 3. (20%)

With the adjustment of the resistor R<sub>L</sub> in the circuit of Fig.3, the maximum power delivered to R<sub>L</sub> can be achieved. Please calculate the maximum power transferred to R<sub>L</sub>?

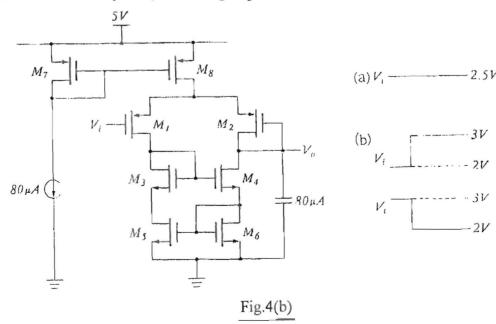

## 4. (20%)

A differential to single-ended amplifier is constructed as shown in Fig.4(a). The amplifier

編號:

165

國立成功大學一○○學年度碩士班招生考試試題

共 3 頁 第2頁

系所組別: 奈米科技暨微系統工程研究所

考試科目: 電子電路學

考試日期:0219,節次:1

# ※ 考生請注意:本試題 □可 四不可 使用計算機

incorporates Wilson current mirror as active loads. Assuming all of the transistors are in saturation,  $\mu_n C_{o\chi} = 80\mu A/V^2$ ,  $\mu_p C_{o\chi} = 30\mu A/V^2$ ,  $|V_T| = 0.8V$  for both NMOS and PMOS, (W/L) MI = (W/L) M2 = 320/0.6, (W/L) M3 = (W/L) M4 = (W/L) M5 = (W/L) M6 = 20/0.9, (W/L) M7 = 80/0.6, (W/L) M8 = 160/0.6. Neglect channel length modulation effect.

- (a) What kind of feedback mechanism is applied in the Wilson current mirror? (shunt-shunt, series-series, shunt series, series- shunt)

- (b) Find out the input common mode ranges V<sub>icm(max)</sub>, √<sub>icm(min)</sub> of this amplifier.

- (c) Consider the circuit shown in Fig.4(b). Assume that  $(W/L)_{M3} = (W/L)_{M6} = 21/0.9$ ,  $(W/L)_{M4} = (W/L)_{M5} = 19/0.9$ , and the other derives' sizes remain unchanged. If  $V_i$ =2.5V, find  $V_0$ . (The OP's input offset voltage must be taken into account).

- (d) Follow (c) and neglect all the parasitic capacitances of MOSFETs. If  $V_i$  is a rising step from 2V to 3V, find the slew rate of  $V_o$ . If  $V_i$  is a falling step from 3V to 2V, find the slew rate of  $V_o$ .

編號:

165

國立成功大學一○○學年度碩士班招生考試試題

共 3 頁,第3頁

系所組別: 奈米科技暨微系統工程研究所

考試科目: 電子電路學

考試日期:0219,節次:1

※ 考生請注意:本試題 □可 □不可 使用計算機

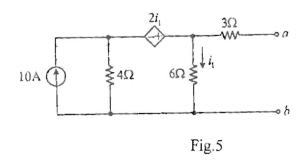

## 5. (15%)

Please find the Thévenin and Norton equivalent circuits of the network of Fig.5 at terminals a-b.

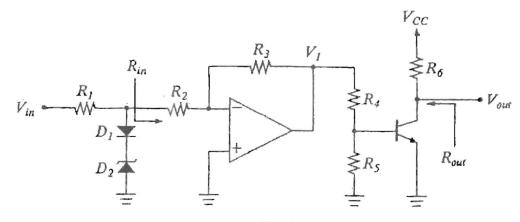

## 6. (15%)

In the circuit as shown in Fig.6, the junction diode  $D_1$  can be modeled by a forward constant voltage drop of  $V_r$ =0.7V; the Zener diode  $D_2$  can be modeled by an ideal Zener voltage of  $V_z$ =3.3V; the op-amp is ideal; the BJT has parameters  $\beta$ =50,  $V_{BE(on)}$ =0.7V,  $V_A$ = $\infty$ ,  $V_{CE(sat)}$ =0.5V. The resistors are  $R_1$ = $R_2$ = $R_3$ = $R_4$ = $R_5$ =1k $\Omega$ ,  $R_6$ =50 $\Omega$ . The supply voltage is  $V_{CC}$ =12V

- (a) Find the voltage  $V_I$  for  $V_{in}$ =-10V, -5V, 5V, and 10V.

- (b) Derive the expression for  $V_{out}$  as function of  $V_{I}$ .

- (c) Find the value for Rin and Rout.

Fig.6