## 89 學年度 國立成功大學 系 電子學 試題 共 2 頁 領士班招生考試 微電子工程 所 電子學 試題 第 1 頁

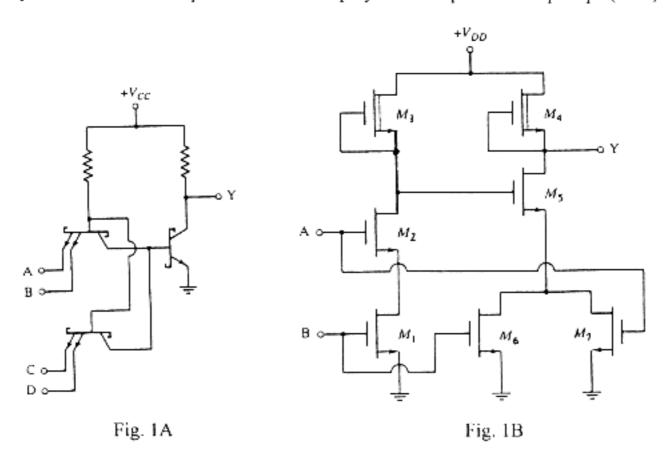

- (a) Determine the logic function at the output Y of the circuit shown in Fig. 1A.

(10%)

- (b) What is the logic function realized at Y in the NMOS circuit shown in Fig. 1B? (10%)

- Using the ideal op amp to implement two different non-inverting integrators without inverter. Explain your results in brief. (10%)

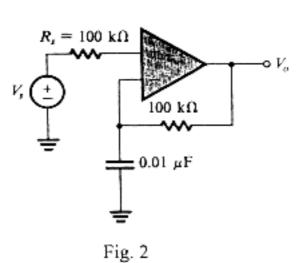

- 3. The op amp in the circuit of Fig. 2 has an open-loop gain of  $10^5$  and a single-pole rolloff with  $\omega_{3dB}=10$  rad/s.

- (a) Sketch a Bode plot for the loop gain. (2%)

- (b) Find the frequency at which  $|A\beta| = 1$ , and find the corresponding phase margin. (4%)

- (c) Find the closed-loop transfer function, including its zero and poles. (4%)

- 4. Why is Miller-effect compensation often employed to compensate an op amp? (10%)

(背面仍有题目,請繼續作答)

## 89 學年度 國立成功大學 系 電子學 試題 共 2 頁 碩士班招生考試 微電子工程 所 電子學 試題 第 2 頁

- Draw the circuit diagram of a 2-bit charge-redistribution A/D converter and explain its operational principle. (10%)

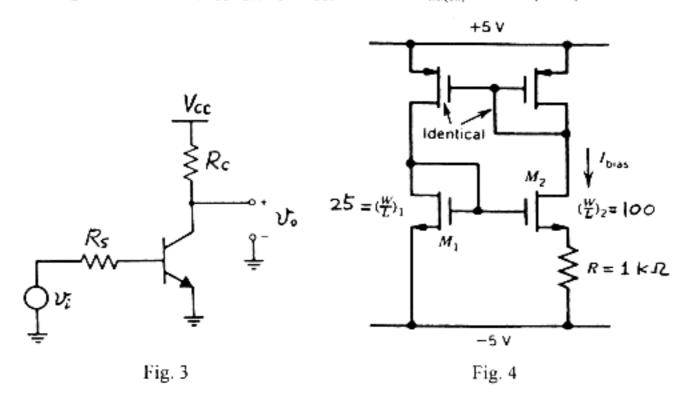

- 6. The circuit of an amplifier is shown in Fig. 3.

- (a) Express the overall small-signal gain v<sub>o</sub>/v<sub>i</sub> as a function of R<sub>S</sub>, R<sub>C</sub>, β, V<sub>A</sub>, and collector current I<sub>C</sub>. (10%)

- (b) Assume that  $R_S = R_C = 50K\Omega$ ,  $\beta = 200$ ,  $V_A = 120V$ , determine the value of dc collector bias current  $I_C$  that maximizes  $v_o/v_i$  (10%).

- 7. Calculate the bias current  $I_{bias}$  of the circuit shown in Fig. 4. Assume that threshold voltage of M1 and M2 is identical,  $\mu_n C_{ox} = 20 \mu A/V^2$ . (10%)

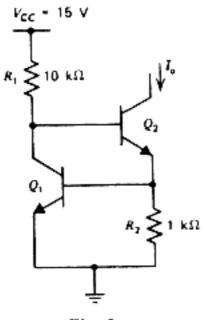

- 8. Calculate the value of sensitivity S of output current to supply voltage for the circuit of Fig. 5, where  $S = (V_{CC}/I_o)(\partial I_o/\partial V_{CC})$ . Assume  $V_{BE(on)} = 0.7V$ . (10%)

Fig. 5