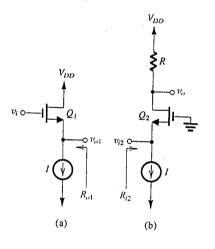

- 1. (a) For the source follower in Fig.1 (a), find the open-circuit voltage gain  $v_{ol}/v_i$  and the output resistance  $R_{0l}$ , in terms of  $g_{ml}$  and  $\chi$ . Neglect the effect of  $r_{ol}$  and that of the output resistance of the bias current source.  $g_{mb} = \chi g_m$ ,  $g_{mb}$  is the body transconductance.

- (b) For the common-gate amplifier in Fig,1(b), find the voltage gain  $v_o/v_{i2}$  and the input resistance  $R_i$ , in terms of  $g_{m2}$ ,  $\chi$ , and R. Neglect the effect of  $r_{02}$  and that of the output resistance of the bias current source.

- (c) If the output terminal of the source follower in (a) is connected to the input terminal of common-gate amplifier in (b), find the overall voltage gain  $v_o/v_i$  of the cascaded amplifier.

- (d)If  $V_{DD} = 5$  V and the dc bias voltage at the drain of  $Q_2$  is to be 0 V, find the effective voltage ( $V_{GS} V_t$ ) required for  $Q_1$  and  $Q_2$  so that an overall voltage gain of 25 V/V is realized.

- (e)For I = 50  $\mu$  A and k  $_n$  =  $\mu$   $_n$ C<sub>OX</sub>=50  $\mu$  A/V<sup>2</sup>, find R and the (W/L) required for Q<sub>1</sub> and Q<sub>2</sub>.(15%)

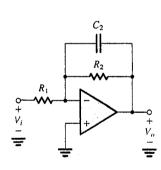

- 2. As the circuit shown in Fig. 2, design the circuit to obtain a dc gain of 40 dB, a 3-dB frequency of 1.5 KHz., and an input resistance of 1 K $\Omega$ . At what frequency does the magnitude of transmission become unity? What is the phase angle at this frequency? Assume op amp is ideal.(10%)

Fig. 1

Fig. 2

- 3. (a)List five characteristics of an amplifier that are modified by negative feedback. (10%)

- (b) Draw the circuit diagram of a switched-capacitor (SC) integrator. (5%)

- (c) Derive the time constant of a SC integrator. (5%)

- (d) Briefly explain why the time constant of a SC circuit can be well controlled. (5%)

- 4. If the collector current of a BJT operated in forward active region is expressed as  $i_C = (av_{BE}^2 + bv_{BE})(1 + cv_{CE}) \approx \beta i_B$ ,

where a, b, c, and  $\beta$  are constant, derive and sketch its small-signal equivalent circuit for the cases of (a) c = 0 and (b)  $c \neq 0$ . (10%)

(背面仍有題目,請繼續作答)

## 90 學年度 國立成功大學 系 重多学 試題 共 2 頁 碩士班招生考試 然表子 於 所 第 2 頁

- 5. (a) Design a MOSFET current mirror to provide currents of  $I_o$  and  $I_o/2$  simultaneously, where  $I_o$  is a constant. (5%)

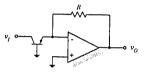

- (b) Derive the transfer characteristics (i.e.,  $v_O v_I$  relation) of the circuit shown in Fig. 3. Assume the Op-Amp is ideal. (5%)

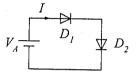

- (c) Draw the load line of the diode  $D_2$  shown in Fig. 4 and find I graphically. Assume  $D_1$  and  $D_2$  are identical diodes,  $V_A = 1.5V_\gamma$ , where  $V_\gamma$  is the cut-in voltage of the diode. (5%)

Fig. 3

Fig. 4

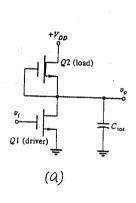

6. An inverter circuit is shown in Fig. a. The output current-voltage characteristics of transistors Q1 and Q2, and the transfer characteristics of this inverter are shown in Fig. b, c, and d, respectively. Assume that C<sub>tot</sub>=0.3pF and the input signal has V(0)=0.3V and V(1)=6V. Please determine the values of the propagation delay t<sub>PHL</sub> and t<sub>PLH</sub>. (25%)

$V_{GS1} = 6.0 \text{ V}$ 300

250

5.5

100

4.5

Load line

3.5

3.0

2.5  $V_{DS1}$ , v

(b)