系所組別 平電科學與工程研究所乙組

考試科目 電子學

秦欽日期:0306 新次:1

## ※ 考生請注意 本試題 □可 □不可 使用計算機

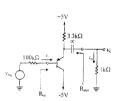

For the current mirror in the right figure derive an expression for the current transfer function [459/46] taking into account the BIT internal capacitances and neglecting r<sub>s</sub> and r<sub>s</sub>. Assume the BJTs to be identical, Observe that a signal ground appears at the collector of Q<sub>s</sub>. If the mirror is biased at 1mA and the BJTs at this operating point are characterized by f<sub>1</sub>=400MHz,

$C_s=2pF$ , and  $\beta_0=\infty$ , find (a)the frequencies of the pole  $(f_p)$  of the transfer function.  $f_p=$  (7% (b)the frequencies of the zero  $(f_p)$  of the transfer function.  $f_p=$  (6%

2. For the emitter follower in the right figure, the signal source is directly coupled to the transistor base. If the dc component of v<sub>nk</sub> is zero, (a) find the dc emitter current (5%) is Assume [8=100. Neglecting 1<sub>m</sub>. (b) find R<sub>m</sub>. (5%), (c) the voltage gain v<sub>nk</sub>(v<sub>nk</sub>(5%), (d) the current gain v<sub>nk</sub>(v<sub>nk</sub>(5%), and (e) the output resistance R<sub>m</sub>. (5%)

3. In the below figure, transistors  $Q_1$  and  $Q_2$  have  $V_1$ =1V, and the process transconductance parameter  $k_n$ '=100 $\mu$ A/V<sup>2</sup>, Assuming  $\lambda$ =0, find  $V_1$ ,  $V_2$ , and  $V_3$  for  $(W/L)_1$ =1.5(W/L)<sub>2</sub>, (12%)

$$\begin{array}{c} +5V \\ \hline 40k\Omega \\ \hline V_1 \bullet & V_2 \\ \hline \end{array}$$

系所組別: 光電科學與工程研究所乙組

考試科目: 電子學

#EE:

考試日期:0306・軽次:1

## ※ 考生請注意:本試類 □ □ □ 不可 使用計算機

4.(a)Use the superposition principle to find the output voltage of the circuit shown in Fig.1.(b) If in the circuit of Fig.1 the 1-k $\Omega$  resistor is disconnected from ground and connected to a third signal source  $\nu_3$ , use superposition to determine  $\nu_0$  in term of  $\nu_1$ ,  $\nu_2$  and  $\nu_1$ (10%)

- 5. Consider a Si n-channel MOSFET with channel width  $W=15~\mu m$ , length  $L=2~\mu m$ , gate oxide thickness  $t_{cs}=0.5~\mu m$ , dielectric constant  $t_{cs}=3.9$ . Assume that the drain current in the saturation region for  $V_{DS}=0.10V$  is  $I_D=3.5mA$  at  $V_{GS}=1.5V$  and  $I_D=75~mA$   $V_{GS}=2.5V$ . (a)Please find the inversion carrier mobility  $(\mu_a)$  in channel and the threshold voltage( $V_T$ ). (b)please comment the determined  $\mu_a$  compared with the bulk mobility.(10%)

- 6. As shown in Figure 2, if the five light output power-current (L-I) curves correspond to a GaAs LED operated at different pulsed injection currents, i.e., different duty cycles, which is defined in the inset of Figure 2. Please identify which of the following item(s) is/are) true.(A)duty1> duty 2(B) duty 3> duty 4(C) duty 2> duty 5(D) duty 3> duty 2(E) duty 5> duty 4(2%)

#4 百,第7百

系所組別: 光雷科學與工程研究所乙組

細跡:

考試科目: 電子學 考試日期:0306·動次:1

※ 考生請注意:本試願 □可 □不可 使用計算機

Under thermal equilibrium, which of the following approache(s) can create a built-in electric field in a semiconductor?(A)p-n junction(B) spatial variation of doping concentration(C)n-type GaAs(D)intrinsic Si.(2%)

8. The zener diode in the circuit of Figure 3 is specified to have  $V_Z$ =6.8V at  $I_Z$ =5  $mA.r_z=20 \Omega$  and  $I_{zt}=0.2 mA$ . The power supply voltage  $V^+=10V$ .

(A)  $V_0 = 6.83$  V with no load (B)  $I_1 = 13.6$  mA when  $R_1 = 0.5$ K $\Omega$ (C)  $V_0 = 5$  V when  $R_1 = 0.5K\Omega$  (D)  $I_z = 6.35$  mA with no load (6%)

- 9. The threshold voltage will increase for a n-channel MOS FET when (A)increase the reverse bias of substrate increase (B) decrease the doping concentration of substrate (C)increase the thickness of gate oxide (D) increase the gate length. (3%)

- 10. Which of the following statement(s) is/are) true(A)The BJT transconductance increases exponentially with respect to V<sub>BF</sub>.(B)The MOS FET's transconductance increases linearly with respect to VGS.(C)A PMOS FET has four terminals(D)Compared with MOS FET, BJT device has higher input impedance. (3%)

編號: 44

## 國立成功大學九十九學年度碩士班招生考試試題

共 4 頁 第 4 頁

系所組別 光電科學與工程研究所乙組

考試科目: 電子學

考試日期:0306·箭次:1

## ※ 考生請注意:本試題 ☑可 □不可 使用計算機

- 11. Please identify the following schematic device.

- (a)\_\_\_\_(2%)

(b) (2%)

12. Determine the output voltage  $V_0$  in the following circuit when (a)  $V_1{=}V_2{=}5V$  (5%)(b)  $V_1{=}$  5V,  $V_2{=}0$ . Assume that the  $D_1$  is identical to  $D_2$  with  $r_D{=}30~\Omega$ ,  $V_{D0}{=}0.6V(5\%)$